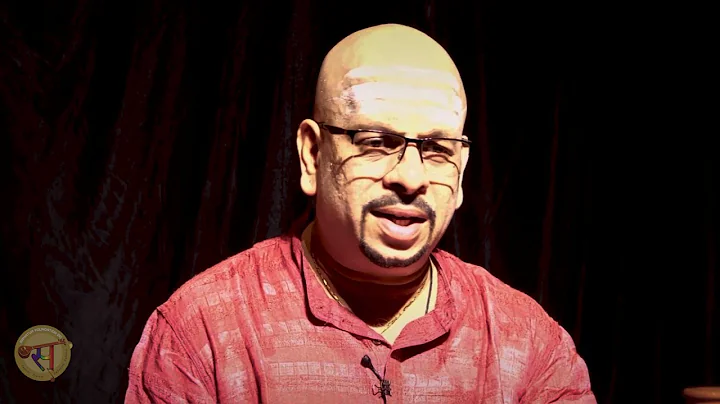

Suresh K Venkumahanti

age ~56

from Austin, TX

- Also known as:

-

- Su Venkumahanti

- Phone and address:

-

1810 San Gabriel St, Austin, TX 78701

5124789003

Suresh Venkumahanti Phones & Addresses

- 1810 San Gabriel St, Austin, TX 78701 • 5124789003

- 807 30Th St, Austin, TX 78705 • 5124760998

- 7150 Grand Ave, Dallas, TX 75223

- Gainesville, FL

- 214 NW 14Th St, Gainesville, FL 32603

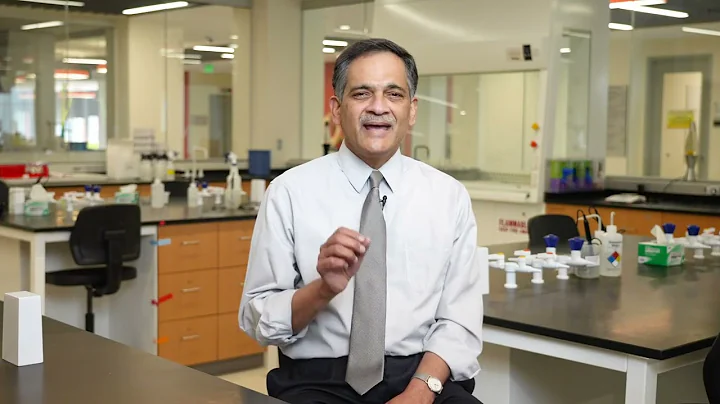

Work

-

Company:QualcommJun 2016

-

Position:Senior director, technology

Education

-

Degree:Associate degree or higher

Skills

Processors • Logic Design • Low Power Design • Asic • Verilog • Rtl Design • Soc • Debugging • X86 • Microarchitecture • Embedded Systems • Multithreading

Industries

Wireless

Name / Title

Company / Classification

Phones & Addresses

Director

CENTRAL TEXAS VIPASSANA ASSOCIATION, INC

Business Services at Non-Commercial Site · Nonclassifiable Establishments

Business Services at Non-Commercial Site · Nonclassifiable Establishments

1810 San Gabriel St, Austin, TX 78701

Resumes

Senior Director, Technology

view sourceLocation:

Austin, TX

Industry:

Wireless

Work:

Qualcomm

Senior Director, Technology

Qualcomm

Principal Engineer and Manager

Freescale Semiconductor Dec 1999 - Jan 2005

Staff Engineer

Cyrix Sep 1997 - Nov 1999

Senior Engineer

Amd Sep 1996 - Nov 1997

Product Engineer

Senior Director, Technology

Qualcomm

Principal Engineer and Manager

Freescale Semiconductor Dec 1999 - Jan 2005

Staff Engineer

Cyrix Sep 1997 - Nov 1999

Senior Engineer

Amd Sep 1996 - Nov 1997

Product Engineer

Skills:

Processors

Logic Design

Low Power Design

Asic

Verilog

Rtl Design

Soc

Debugging

X86

Microarchitecture

Embedded Systems

Multithreading

Logic Design

Low Power Design

Asic

Verilog

Rtl Design

Soc

Debugging

X86

Microarchitecture

Embedded Systems

Multithreading

Us Patents

-

Method And System For A Digital Signal Processor Debugging During Power Transitions

view source -

US Patent:7657791, Feb 2, 2010

-

Filed:Nov 15, 2006

-

Appl. No.:11/560323

-

Inventors:Lucian Codrescu - Austin TX, US

William C. Anderson - Austin TX, US

Suresh Venkumahanti - Austin TX, US

Louis Achille Giannini - San Diego CA, US

Manojkumar Pyla - San Diego CA, US

Xufeng Chen - San Diego CA, US -

Assignee:QUALCOMM Incorporated - San Diego CA

-

International Classification:G06F 11/00

-

US Classification:714 30, 714 31

-

Abstract:Techniques for the design and use of a digital signal processor, including (but not limited to) for processing transmissions in a communications (e. g. , CDMA) system. A method and system control transferring data between debugging registers and digital signal processor processes in association with a power transition sequence of the digital signal processor. In a digital signal processor, debugging registers associate with the core processor process and the debugging process. Control bits control transferring data among the debugging registers, the core processor process and the debugging process. The control bit prevents transferring data among the debugging registers, the core processor process and the debugging process in the event of a power transition sequence. Control bits also prevent a power transition sequence of the digital signal processor in the event of transferring data among the debugging registers and the core processor process or the debugging process.

-

System And Method Of Using An N-Way Cache

view source -

US Patent:7827356, Nov 2, 2010

-

Filed:Sep 10, 2007

-

Appl. No.:11/852348

-

Inventors:Suresh Venkumahanti - Austin TX, US

Phillip Matthew Jones - Round Rock TX, US -

Assignee:QUALCOMM Incorporated - San Diego CA

-

International Classification:G06F 12/00

-

US Classification:711128, 711125, 711156, 711159, 711202, 711221

-

Abstract:A system and method of using an n-way cache are disclosed. In an embodiment, a method includes determining a first way of a first instruction stored in a cache and storing the first way in a list of ways. The method also includes determining a second way of a second instruction stored in the cache and storing the second way in the list of ways. In an embodiment, the first way may be used to access a first cache line containing the first instruction and the second way may be used to access a second cache line containing the second instruction.

-

Completion Continue On Thread Switch Based On Instruction Progress Metric Mechanism For A Microprocessor

view source -

US Patent:7941646, May 10, 2011

-

Filed:Dec 31, 2007

-

Appl. No.:11/967430

-

Inventors:David C. Holloway - Cedar Park TX, US

Michael D. Snyder - Cedar Park TX, US

Suresh Venkumahanti - Austin TX, US -

Assignee:Freescale Semicondoctor, Inc. - Austin TX

-

International Classification:G06F 9/00

-

US Classification:712220

-

Abstract:A thread switch mechanism and technique for a microprocessor is disclosed wherein a processing of a first thread is completed, and a continuation of a second thread is initiated during completion of the first thread. In one form, the technique includes processing a first thread at a pipeline of a processing device, and initiating processing of a second thread at a front end of the pipeline in response to an occurrence of a context switch event. The technique can also include initiating a instruction progress metric in response the context switch event. The technique can further include enabling completion of processing of instructions of the first thread that are at a back end of the pipeline at the occurrence of the context switch event until an expiry of the instruction progress metric.

-

System And Method Of Selectively Accessing A Register File

view source -

US Patent:7979681, Jul 12, 2011

-

Filed:Nov 20, 2007

-

Appl. No.:11/943190

-

Inventors:Suresh K. Venkumahanti - Austin TX, US

Lucian Codrescu - Austin TX, US

Shankar Krithivasan - Austin TX, US

Jian Shen - Austin TX, US

Lin Wang - Austin TX, US -

Assignee:QUALCOMM Incorporated - San Diego CA

-

International Classification:G06F 9/00

-

US Classification:712225, 712223

-

Abstract:In a particular embodiment, a method is disclosed that includes identifying a first block of bits within a result to be written to a destination register by an execution unit. The result includes a plurality of bits having the first block of bits and a second block of bits. The first block of bits has a value of zero. The method further includes providing an encoded bit value representing the first block of bits to a control register and selectively writing the second block of bits, but not the first block of bits, to the destination register. The destination register is sized to receive the first and second blocks of bits.

-

Shared Interrupt Controller For A Multi-Threaded Processor

view source -

US Patent:7984281, Jul 19, 2011

-

Filed:Dec 12, 2007

-

Appl. No.:11/954615

-

Inventors:Erich James Plondke - Austin TX, US

Lucian Codrescu - Austin TX, US

Muhammad Ahmed - Dallas TX, US

William Anderson - Austin TX, US

Suresh K. Venkumahanti - Austin TX, US -

Assignee:QUALCOMM Incorporated - San Diego CA

-

International Classification:G06F 9/00

-

US Classification:712244, 710260, 710261

-

Abstract:A multi-threaded processor is disclosed that includes a sequencer adapted to provide instructions associated with one or more threads of a multi-threaded processor. The sequencer includes an interrupt controller adapted to receive one or more interrupts and to selectively allow a first thread of the one or more threads to service at least one interrupt. The interrupt controller includes logic to preclude a second thread of the one or more threads from responding to the at least one interrupt.

-

Multithreaded Processor With Lock Indicator

view source -

US Patent:8140823, Mar 20, 2012

-

Filed:Dec 3, 2007

-

Appl. No.:11/949284

-

Inventors:Lucian Codrescu - Austin TX, US

Erich James Plondke - Austin TX, US

Suresh Venkumahanti - Austin TX, US -

Assignee:QUALCOMM Incorporated - San Diego CA

-

International Classification:G06F 12/10

-

US Classification:711207, 711208, 711145, 711E12058

-

Abstract:Systems and methods including a multithreaded processor with a lock indicator are disclosed. In an embodiment, a system includes means for indicating a lock status of a shared resource in a multithreaded processor. The system includes means for automatically locking the shared resource before processing exception handling instructions associated with the shared resource. The system further includes means for unlocking the shared resource.

-

System And Method Of Data Forwarding Within An Execution Unit

view source -

US Patent:8145874, Mar 27, 2012

-

Filed:Feb 26, 2008

-

Appl. No.:12/037300

-

Inventors:Suresh Venkumahanti - Austin TX, US

Lucian Codrescu - Austin TX, US

Lin Wang - Austin TX, US -

Assignee:QUALCOMM Incorporated - San Diego CA

-

International Classification:G06F 12/10

G06F 9/34 -

US Classification:711202, 711169, 711217, 711E12061, 712218

-

Abstract:In an embodiment, a method is disclosed that includes, comparing, during a write back stage at an execution unit, a write identifier associated with a result to be written to a register file from execution of a first instruction to a read identifier associated with a second instruction at an execution pipeline within an interleaved multi-threaded (IMT) processor having multiple execution units. When the write identifier matches the read identifier, the method further includes storing the result at a local memory of the execution unit for use by the execution unit in the subsequent read stage.

-

System And Method To Access A Portion Of A Level Two Memory And A Level One Memory

view source -

US Patent:8341353, Dec 25, 2012

-

Filed:Jan 14, 2010

-

Appl. No.:12/687552

-

Inventors:Suresh K. Venkumahanti - Austin TX, US

Christopher Edward Koob - Round Rock TX, US

Lucian Codrescu - Austin TX, US -

Assignee:QUALCOMM Incorporated - San Diego CA

-

International Classification:G06F 12/08

-

US Classification:711122, 711120, 711E12042, 711E12043

-

Abstract:A system and method to access data from a portion of a level two memory or from a level one memory is disclosed. In a particular embodiment, the system includes a level one cache and a level two memory. A first portion of the level two memory is coupled to an input port and is addressable in parallel with the level one cache.

Youtube

Get Report for Suresh K Venkumahanti from Austin, TX, age ~56